# DARE - radiation hardening by design

## **Product Overview**

DARE22G IVREF18 implements a bandgap-based reference voltage and current generator for radiationhardened applications in the commercial GF 22 nm FDSOI CMOS technology.

This IP supports a range of DARE22G platform IP blocks that require on-chip current and/or voltage biasing, such as LVDS, BBG, and OSC100M.

### Features

DARE22G IVREF18 main functionalities include:

- 0.6 V and 1.25 V (±1%) reference voltages

- 10 high-precision 10 µA sinking current sources

- 9 internal biasing current sources for extra reference voltage generation

- Excellent stability over supply voltage, load variation and temperature

- Low operating current (< 420 μA)</li>

- Digital calibration

- Power-down mode (< I µA)

- TID immunity over 100 krad (SiO<sub>2</sub>)

- SET immunity over 60 MeV.cm<sup>2</sup>/mg

- SEL immunity over 70 MeV.cm<sup>2</sup>/mg

## **Block Diagram**

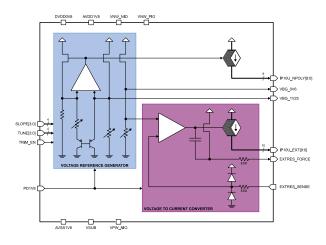

The IVREF18 macro comprises a bandgap circuit, current mirrors, and a voltage-to-current converter. The bandgap circuit generates 0.6 V and 1.25 V reference voltage signals. Digital calibration for voltage offset and temperature drift can be performed using trimming codes provided via TUNE[3:0] and SLOPE[3:0] input buses. Calibration is enabled when the TRIM\_EN input is set to logical I upon start-up.

The internally generated reference voltage signals are used by the voltage-to-current converter to produce the high-precision 10  $\mu$ A current sources, which are output via the IP10U\_EXT[9:0] bus. This conversion requires an external accurate pull-down resistor connected to both EXTRES\_FORCE and EXTRES\_SENSE pins.

In contrast, internal biasing current sources offer a fully integrated alternative that is more sensitive to PVT variations, where no external components are required. These current sources replicate the internal bandgap biasing current to generate a coarse 10  $\mu$ A internal biasing current sources delivered via the IP10U NPOLY[8:0] bus.

The internal biasing current sources can also be used to generate up to nine replicas of the reference voltage when connected to dedicated NPOLY resistors.

## I.8 V Current & Voltage Reference

Product Brief

DARE22G

## **Pin Interface**

| Pin Name         | Туре    | Description                                          |  |  |

|------------------|---------|------------------------------------------------------|--|--|

| AVDDIV8          | Power   | Analog power supply                                  |  |  |

| DVDD0V8          | Power   | Digital power supply                                 |  |  |

| AVSSIV8          | Ground  | Ground supply                                        |  |  |

| VSUB             | Ground  | P-substrate bias voltage                             |  |  |

| VNW_PIO          | Power   | Back-bias voltage for reversed-biased NMOS           |  |  |

| VNW_NIO          | Power   | Back-bias voltage for<br>forward-biased NMOS         |  |  |

| VPW_NIO          | Ground  | Back-bias voltage for reversed-biased PMOS           |  |  |

| VBG_0V6          | Analog  | 0.6 V reference voltage                              |  |  |

| VBG_IV25         | Analog  | 1.25 V reference                                     |  |  |

|                  | -       | voltage                                              |  |  |

| IP10U_NPOLY[8:0] | Analog  | 10 μA internal biasing                               |  |  |

|                  |         | current sources                                      |  |  |

| IP10U_EXT[9:0]   | Analog  | 10 μA high-precision<br>current sources              |  |  |

| EXTRES_FORCE     | Analog  | External 12 k $\Omega$ resistor low-ohmic connection |  |  |

| EXTRES_SENSE     | Analog  | External 12 k $\Omega$ resistor sensing connection   |  |  |

| PD1V8            | Digital | Power-down enable                                    |  |  |

| TUNE[3:0]        | Digital | Reference voltage's                                  |  |  |

|                  | -       | offset trimming bits                                 |  |  |

| SLOPE[3:0]       | Digital | Reference voltage's                                  |  |  |

|                  |         | temperature slope                                    |  |  |

|                  |         | trimming bits                                        |  |  |

| TRIM_EN          | Digital | Trimming enable                                      |  |  |

## **Physical Dimensions**

DARE22G IVREF18 is implemented as a core macro.

| IP Name | Width  | Height |

|---------|--------|--------|

| IVREF18 | 526 µm | 220 µm |

#### Contact

For further information, please contact us at <u>dare@imec.be</u>

## **Operating Conditions**

Performance and reliability are not guaranteed outside these recommended operating boundaries.

| Parameter              | Name               | Minimum | Typical | Maximum | Unit                     |

|------------------------|--------------------|---------|---------|---------|--------------------------|

| Digital supply voltage | V <sub>DD0V8</sub> | 0.72    | 0.8     | 0.88    | V                        |

| Analog supply voltage  | V <sub>DDIV8</sub> | 1.62    | 1.8     | 1.98    | V                        |

| Operating temperature  | TI                 | -40     | 25      | 125     | °C                       |

| ESD rating (HBM)       | V <sub>HBM</sub>   | 2       |         |         | kV                       |

| TID immunity           | TID                | 100     |         |         | krad (SiO <sub>2</sub> ) |

| SET hardening          | $SET_{th}$         | 60      |         |         | MeV.cm <sup>2</sup> /mg  |

| SEL hardening          | SEL <sub>th</sub>  | 70      |         |         | MeV.cm <sup>2</sup> /mg  |