# DARE - radiation hardening by design

# **Product Overview**

DARE22G PLL implements a complete radiationhardened phase-locked loop IP in the commercial GF 22 nm FDSOI CMOS technology.

Radiation and single-event effects are mitigated by using various radiation-hardened-by-design (RHBD) techniques. Strong drive-strength gates, SET filters and TMR are used in digital circuitry whereas redundancy techniques and RC filters are employed in analog blocks.

### Features

DARE22G PLL main functionalities include:

- Wide output frequency range from 1.953 MHz up to 3 GHz

- Wide input frequency range from 20 MHz up to 800 MHz

- Programmable input and output clock dividers

- Built-in clock generation bypassing

- Built-in digital lock detection

- Low RMS period jitter below I ps

- Power-down mode (< 7 μA)</li>

- Maximum current consumption below 30 mA

- SET immunity over 60 MeV.cm<sup>2</sup>/mg

- SEL immunity over 70 MeV.cm<sup>2</sup>/mg

- TID tolerance over 100 krad (SiO<sub>2</sub>)

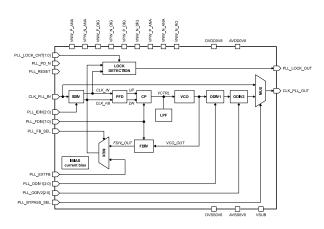

# **Block Diagram**

The core of the PLL is composed of a TMR-hardened VCO, a programmable charge pump synchronized with a feedback frequency divider, a PFD, and a second-order LPF. A current bias circuit provides a reference current to the charge pump.

The input clock signal is scaled by the input divider (IDIV) to match the feedback clock signal frequency which is derived from the VCO clock signal after the feedback divider (FDIV) in the PLL core. These two signals are inputs to both the PFD and the lock detection circuit.

The digital lock detection mechanism provides an output flag signal that raises to 1 when input and output clock signals are phase-synchronized.

Two additional dividers (ODIVI & ODIV2) connected in series are used to derive the output clock signal from the VCO output at the desired frequency.

A multiplexer before the clock output pin allows the selection between the generated clock and the input clock signals via an input control signal. Bypassing the generated clock may be useful during initialization or reconfiguration to wait until lock state is achieved.

# **Pin Interface**

| PLL_FDIV[7:0]   Digital   Selection bits for FDIV's division factor     PLL_IDIV[2:0]   Digital   Selection bits for IDIV's division factor     PLL_LOCK_CNT   Digital   Lock detection counter selection bits     [1:0]   Selection bits   Digital     PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for                                                                                                                                                                                                                                                                                                                                                        | AVSSOV8<br>DVDDOV8<br>DVSSOV8<br>CLK_PLL_IN<br>CLK_PLL_OUT<br>PLL_BYPASS_SEL<br>PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0] | Power<br>Ground<br>Power<br>Digital<br>Digital<br>Digital<br>Digital<br>Digital<br>Digital | Analog ground supply<br>Digital power supply<br>Digital ground supply<br>Reference input clock<br>Output clock<br>Bypass-mode enable<br>External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVSS0V8GroundAnalog ground supplyDVDD0V8PowerDigital power supplyDVSS0V8GroundDigital ground supplyDVSS0V8GroundDigital ground supplyCLK_PLL_INDigitalReference input clockCLK_PLL_OUTDigitalOutput clockPLL_BYPASS_SELDigitalBypass-mode enablePLL_EXTFBDigitalExternal feedback clock selectionPLL_FB_SELDigitalFeedback clock selection bits for FDIV's division factorPLL_IDIV[7:0]DigitalSelection bits for IDIV's division factorPLL_LOCK_CNTDigitalLock detection counter selection bitsPLL_ODIV1[2:0]DigitalSelection bits for DigitalPLL_ODIV1[2:0]DigitalSelection bits for PLVPLL_ODIV2[2:0]DigitalSelection bits for PLVPLL_ODIV2[2:0]DigitalSelection bits for PLVPLL_ODIV2[2:0]DigitalSelection bits for                                                                  | DVDD0V8<br>DVSS0V8<br>CLK_PLL_IN<br>CLK_PLL_OUT<br>PLL_BYPASS_SEL<br>PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0]            | Power<br>Ground<br>Digital<br>Digital<br>Digital<br>Digital<br>Digital<br>Digital          | Analog ground supply<br>Digital power supply<br>Digital ground supply<br>Reference input clock<br>Output clock<br>Bypass-mode enable<br>External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's |

| DVDD0V8PowerDigital power supplyDVSS0V8GroundDigital ground supplyCLK_PLL_INDigitalReference input clockCLK_PLL_OUTDigitalOutput clockPLL_BYPASS_SELDigitalBypass-mode enablePLL_EXTFBDigitalExternal feedback clock selectionPLL_FB_SELDigitalFeedback clock selection bits for FDIV's division factorPLL_IDIV[7:0]DigitalSelection bits for IDIV's division factorPLL_LOCK_CNTDigitalLock detection counter selection bitsPLL_OCK_OUTDigitalLock detection flagPLL_ODIV1[2:0]DigitalSelection bits for CUIV's division factorPLL_ODIV2[2:0]DigitalSelection bits for CUIV's division factor | DVSS0V8<br>CLK_PLL_IN<br>CLK_PLL_OUT<br>PLL_BYPASS_SEL<br>PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0]                       | Ground<br>Digital<br>Digital<br>Digital<br>Digital<br>Digital<br>Digital                   | Digital power supply<br>Digital ground supply<br>Reference input clock<br>Output clock<br>Bypass-mode enable<br>External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's                         |

| DVSS0V8GroundDigital ground supplyCLK_PLL_INDigitalReference input clockCLK_PLL_OUTDigitalOutput clockPLL_BYPASS_SELDigitalBypass-mode enablePLL_FB_SELDigitalExternal feedback clock selectionPLL_FB_SELDigitalFeedback clock selection bits for FDIV's<br>division factorPLL_IDIV[7:0]DigitalSelection bits for IDIV's<br>division factorPLL_LOCK_CNTDigitalLock detection counter<br>selection bitsPLL_OCK_OUTDigitalLock detection flagPLL_ODIV1[2:0]DigitalSelection bits for<br>gitalPLL_ODIV1[2:0]DigitalSelection bits for<br>gelection bitsPLL_ODIV2[2:0]DigitalSelection bits for<br>gelection bits for<br>gelection bits for                                                                                                                                                 | CLK_PLL_IN<br>CLK_PLL_OUT<br>PLL_BYPASS_SEL<br>PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0]                                  | Digital<br>Digital<br>Digital<br>Digital<br>Digital<br>Digital                             | Digital ground supply<br>Reference input clock<br>Output clock<br>Bypass-mode enable<br>External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's                                                 |

| CLK_PLL_OUTDigitalOutput clockPLL_BYPASS_SELDigitalBypass-mode enablePLL_EXTFBDigitalExternal feedback clockPLL_FB_SELDigitalFeedback clock selectionPLL_FDIV[7:0]DigitalSelection bits for FDIV's<br>division factorPLL_IDIV[2:0]DigitalSelection bits for IDIV's<br>division factorPLL_LOCK_CNTDigitalLock detection counter<br>selection bitsPLL_OCK_OUTDigitalLock detection flagPLL_ODIV1[2:0]DigitalSelection bits for<br>gotalPLL_ODIV2[2:0]DigitalSelection bits for<br>gotal                                                                                                                                                                                                                                                                                                   | CLK_PLL_OUT<br>PLL_BYPASS_SEL<br>PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0]                                                | Digital<br>Digital<br>Digital<br>Digital<br>Digital                                        | Output clock<br>Bypass-mode enable<br>External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's                                                                                                   |

| PLL_BYPASS_SEL   Digital   Bypass-mode enable     PLL_EXTFB   Digital   External feedback clock     PLL_FB_SEL   Digital   Feedback clock selection     PLL_FDIV[7:0]   Digital   Selection bits for FDIV's division factor     PLL_IDIV[2:0]   Digital   Selection bits for IDIV's division factor     PLL_LOCK_CNT   Digital   Lock detection counter selection bits     [1:0]   Selection bits   Selection bits     PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for ODIV1's division factor                                                                                                                                                                 | PLL_BYPASS_SEL<br>PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0]                                                               | Digital<br>Digital<br>Digital<br>Digital                                                   | Bypass-mode enable<br>External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's                                                                                                                   |

| PLL_BYPASS_SEL   Digital   Bypass-mode enable     PLL_EXTFB   Digital   External feedback clock     PLL_FB_SEL   Digital   Feedback clock selection     PLL_FDIV[7:0]   Digital   Selection bits for FDIV's division factor     PLL_IDIV[2:0]   Digital   Selection bits for IDIV's division factor     PLL_LOCK_CNT   Digital   Lock detection counter selection bits     PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for ODIV1's division factor                                                                                                                                                                                                             | PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0]                                                                                 | Digital<br>Digital<br>Digital<br>Digital                                                   | External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's                                                                                                                                         |

| PLL_EXTFB   Digital   External feedback clock     PLL_FB_SEL   Digital   Feedback clock selection     PLL_FDIV[7:0]   Digital   Selection bits for FDIV's division factor     PLL_IDIV[2:0]   Digital   Selection bits for IDIV's division factor     PLL_LOCK_CNT   Digital   Lock detection counter selection bits     I:0]   Selection bits   Selection bits     PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for ODIV1's division factor                                                                                                                                                                                                                    | PLL_EXTFB<br>PLL_FB_SEL<br>PLL_FDIV[7:0]<br>PLL_IDIV[2:0]                                                                                 | Digital<br>Digital                                                                         | External feedback clock<br>Feedback clock selection<br>Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's                                                                                                                                         |

| PLL_FDIV[7:0]   Digital   Selection bits for FDIV's division factor     PLL_IDIV[2:0]   Digital   Selection bits for IDIV's division factor     PLL_LOCK_CNT   Digital   Lock detection counter selection bits     [1:0]   Selection bits   Digital     PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for ODIV1's division factor                                                                                                                                                                                                                                                                                                                                | PLL_FDIV[7:0]                                                                                                                             | Digital                                                                                    | Selection bits for FDIV's<br>division factor<br>Selection bits for IDIV's                                                                                                                                                                                                |

| division factor   PLL_IDIV[2:0] Digital Selection bits for IDIV's division factor   PLL_LOCK_CNT Digital Lock detection counter selection bits   [1:0] Digital Lock detection flag   PLL_LOCK_OUT Digital Lock detection flag   PLL_ODIV1[2:0] Digital Selection bits for ODIV1's division factor   PLL_ODIV2[2:0] Digital Selection bits for                                                                                                                                                                                                                                                                                                                                                                                                                                           | <br>PLL_IDIV[2:0]                                                                                                                         |                                                                                            | division factor<br>Selection bits for IDIV's                                                                                                                                                                                                                             |

| division factor   PLL_LOCK_CNT Digital Lock detection counter selection bits   [1:0] Digital Lock detection flag   PLL_LOCK_OUT Digital Lock detection flag   PLL_ODIV1[2:0] Digital Selection bits for ODIV1's division factor   PLL_ODIV2[2:0] Digital Selection bits for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                           | Digital                                                                                    |                                                                                                                                                                                                                                                                          |

| [1:0]   selection bits     PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LL_LOCK_CNT                                                                                                                               |                                                                                            | division factor                                                                                                                                                                                                                                                          |

| [1:0]   selection bits     PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                           | Digital                                                                                    | Lock detection counter                                                                                                                                                                                                                                                   |

| PLL_LOCK_OUT   Digital   Lock detection flag     PLL_ODIV1[2:0]   Digital   Selection bits for ODIV1's division factor     PLL_ODIV2[2:0]   Digital   Selection bits for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1:0]                                                                                                                                      | 0                                                                                          |                                                                                                                                                                                                                                                                          |

| ODIVI's division factor       PLL_ODIV2[2:0]     Digital     Selection bits for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                           | Digital                                                                                    | Lock detection flag                                                                                                                                                                                                                                                      |

| ODIVI's division factor       PLL_ODIV2[2:0]     Digital     Selection bits for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LL_ODIV1[2:0]                                                                                                                             | Digital                                                                                    | Selection bits for                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                           | -                                                                                          | ODIVI's division factor                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LL_ODIV2[2:0]                                                                                                                             | Digital                                                                                    | Selection bits for<br>ODIV2's division factor                                                                                                                                                                                                                            |

| PLL_PD_N Digital Power-down enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 'LL_PD_N                                                                                                                                  | Digital                                                                                    | Power-down enable                                                                                                                                                                                                                                                        |

| PLL_RESET Digital Reset for digital blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LL_RESET                                                                                                                                  | Digital                                                                                    | Reset for digital blocks                                                                                                                                                                                                                                                 |

| VNW_N_ANA Ground N-well forward-body<br>voltage for analog blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ′NW_N_ANA                                                                                                                                 | Ground                                                                                     |                                                                                                                                                                                                                                                                          |

| VNW_N_DIG Ground N-well forward-body<br>voltage for digital blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 'NW_N_DIG                                                                                                                                 | Ground                                                                                     |                                                                                                                                                                                                                                                                          |

| VNW_N_RO Power N-well forward-body<br>voltage for VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ′NW_N_RO                                                                                                                                  | Power                                                                                      | N-well forward-body                                                                                                                                                                                                                                                      |

| VNW_P_ANA Ground N-well reverse-body<br>voltage for analog blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 'NW_P_ANA                                                                                                                                 | Ground                                                                                     | N-well reverse-body                                                                                                                                                                                                                                                      |

| VNW_P_DIG Power N-well reverse-body<br>voltage for digital blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 'NW_P_DIG                                                                                                                                 | Power                                                                                      | N-well reverse-body                                                                                                                                                                                                                                                      |

| VPW_N_ANA Ground P-well reverse-body<br>voltage for analog blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ′PW_N_ANA                                                                                                                                 | Ground                                                                                     | P-well reverse-body                                                                                                                                                                                                                                                      |

| VPW_N_DIG Ground P-well reverse-body<br>voltage for digital blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ′PW_N_DIG                                                                                                                                 | Ground                                                                                     | P-well reverse-body                                                                                                                                                                                                                                                      |

| VPW_P_ANA Ground P-well forward-body<br>voltage for analog blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PW_P_ANA                                                                                                                                  | Ground                                                                                     | P-well forward-body                                                                                                                                                                                                                                                      |

| VPW_P_DIG Power P-well forward-body<br>voltage for digital blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ′PW_P_DIG                                                                                                                                 | Power                                                                                      | P-well forward-body                                                                                                                                                                                                                                                      |

| VSUB Ground P-substrate bias voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 'SUB                                                                                                                                      | Ground                                                                                     |                                                                                                                                                                                                                                                                          |

## DARE22G Phase-Locked Loop

Product Brief

# **Physical Dimensions**

DARE22G PLL is implemented as a core macro.

| IP Name | Width     | Height |  |

|---------|-----------|--------|--|

| PLL     | I I 40 μm | 603 µm |  |

# **Operating Conditions**

#### Contact

For further information, please contact us at <u>dare@imec.be</u>

Performance and reliability are not guaranteed outside these recommended operating boundaries.

| Parameter              | Name              | Minimum | Typical | Maximum | Unit                     |

|------------------------|-------------------|---------|---------|---------|--------------------------|

| Analog supply voltage  | $V_{AVDD}$        | 0.72†   | 0.8     | 0.88    | V                        |

| Digital supply voltage | $V_{DVDD}$        | 0.72†   | 0.8     | 0.88    | V                        |

| Operating temperature  | T                 | -40     | 25      | 125     | °C                       |

| TID immunity           | TID               | 100     |         |         | krad (SiO <sub>2</sub> ) |

| SET hardening          | SET <sub>th</sub> | 60      |         |         | MeV.cm <sup>2</sup> /mg  |

| SEL hardening          | SEL <sub>th</sub> | 70      |         |         | MeV.cm <sup>2</sup> /mg  |

<sup>†</sup> Minimum analog & digital supply voltage is specified at 0.76 V for maximum VCO frequency of 3 GHz